История развития памяти

Асинхронная память FPM DRAM

Существует довольно много различных вариантов динамической памяти, незначительно отличающихся друг от друга принципами доступа к данным. Обычная динамическая память DRAM уже давно не встречается — в середине 1990-х годов ей на смену пришла модификация динамической памяти FPM DRAM (Fast Page Mode — динамическая память с быстрым страничным доступом).

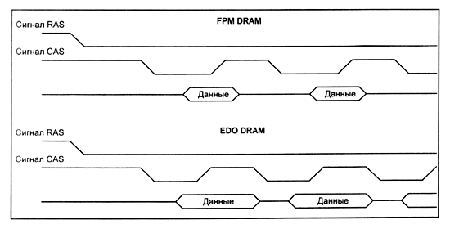

Принцип действия FPM-памяти основан на предположении о последовательном доступе к данным: предполагается, что данные, к которым происходит обращение, расположены последовательно в пределах одной строки матрицы памяти. Страницей в данном случае называется сама строка матрицы. Смысл страничного режима доступа заключается в том, что после выбора строки матрицы и удержания RAS допускается многократная установка адреса столбца, стробируемого СAS. Такой подход позволяет выбирать последовательные данные в пределах одной строки без изменения ее адреса, то есть с одним и тем же сигналом RAS. Это дает возможность ускорить блочные передачи, но только в том случае, если весь блок данных или его часть находится внутри одной строки матрицы.

Асинхронная память EDO DRAM

Вторым типом динамической памяти (она также уже не встречается) является EDO DRAM (Extended Data Out), по сути представляющая собой несколько продвинутый вариант FPM-памяти. В этой памяти тоже реализована страничная схема

доступа, но на выходе микросхемы памяти устанавливаются регистры-защелки данных. При страничном режиме доступа такой тип памяти работает по принципу конвейера: содержимое выбранной ячейки удерживается в выходных регистрах- защелках, в то время как на входы матрицы уже подается адрес следующей выбираемой ячейки. В режиме конвейера удается совместить по времени несколько операций, что приводит к увеличению (по сравнению с FPM-памятью) скорости считывания последовательных массивов данных. Однако при случайной адресации такая память ничем не отличается от обычной.

>

Временная диаграмма работы памяти EDO DRAM

Временная диаграмма работы памяти FPM DRAM

Асинхронная память BEDO DRAM

BEDO (Burst EDO) DRAM — это вариант все той же EDO-памяти, но с реализацией блочного, или пакетного, доступа. В BEDO-памяти реализованы не одиночные циклы чтения/записи данных, а пакетные. Дело в том, что современные процессоры благодаря кэшированию команд и данных обмениваются с оперативной памятью в основном блоками данных. В таком режиме нет необходимости постоянной подачи последовательных адресов на входы микросхем памяти — следует лишь стро- бировать переход к очередному блоку данных отдельным сигналом.

Обращение к BEDO на чтение имеет два отличия от доступа к EDO. Первое — это то, что на выходе устанавливаются триггерные регистры хранения, в соответствии с принципом работы которых в первом такте синхронизирующего импульса (срабатывание по положительному фронту импульса) данные поступают на вход регистра, а во втором такте — на его выход. Тактирующим импульсом в данном случае является сигнал CAS, поэтому в первом такте CAS данные поступают на вход регистров и только во втором такте — на выходы. Преимущество такого внут-

реннего конвейерного звена состоит в том, что во втором такте время появления данных после выдачи переднего фронта CAS будет меньше.

Другое отличие состоит в том, что при обращении к BEDO-памяти задается адрес одной ячейки в строке, а за счет стробирующих импульсов CAS считывается содержание и этой ячейки, и трех следующих, то есть реализуется пакетный метод доступа.